SPECIFICATIONS

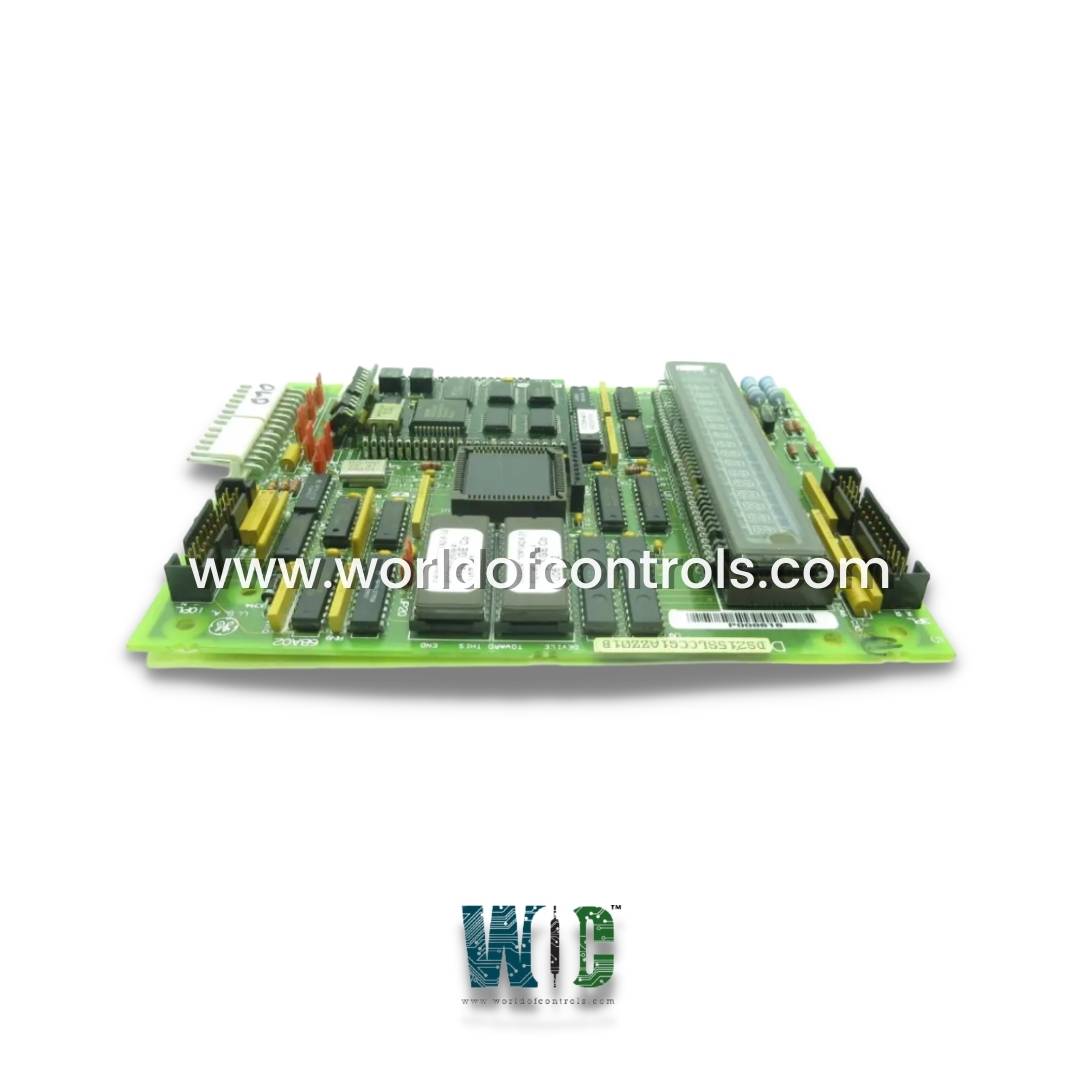

Part Number: DS215SLCCG1AZZ01B

Manufacturer: General Electric

Series: EX2000

Number of relay channels: 12

Product Type: LAN Communications Card

Operating System: QNX

Power supply voltage: 24 V dc

Mounting: DIN-rail mounting

Technology: Surface mount

Operating temperature: 40 to 70 degrees Celsius

Size: 17.8 cm high x 33.02 cm

Repair: 3-7 Day

Availability: In Stock

Country of Manufacturer: United States (USA)

Manual: GEI-100162B

Functional Description

DS215SLCCG1AZZ01B is a LAN Communications Card developed by GE. It is a part of Mark V control system. It has circuits for communications with the drive or exciter that are both isolated and non-isolated. The programmer module is connected to the 16-position alphanumeric display (and display controller, U18). The KPPL connector receives the programmer module, which is mounted to the SLCC. The LAN Control Processor, U1, is the main microprocessor (LCP). Two replaceable EPROMs contain the LCP software (U6 and U7). U8 and U9 supply the LCP-specific Memory. Communication between the LCP and the Drive Control Processor (DCP) on the Drive Control Card occurs via 3PL and dual-ported RAM (U5). Dual-ported RAM [DPR] is RAM set up as memory arrays that two microprocessors may access both independently and concurrently. Mark V improves unit reliability even further by employing three redundant control processors. This triple modular redundant (TMR) design can safely operate, control, and protect a unit in the event that one of its control processors or control processor components fails. The TMR design allows for the shutdown and repair of a single control processor without shutting down the turbine.

Board Connections

Five connectors (marked _PL) connect to the other controller boards, external signals, and the network. These are the connectors to other boards:

- 2PL Connector: This connector is responsible for connecting ±5, 15, and 24 V dc input/output (I/O) signals between various components. The Power Supply/Interface Board (IMCP, DCI, SDCI, or DCFB), the Drive Terminal Board or Simple Drive Terminal Board, and the Drive Control Card establish connections using this connector. It enables the exchange of power and I/O signals required for communication and coordination between these boards.

- 3PL Connector: The 3PL connector is used to connect the inputs from the Drive Control Card. It allows the Drive Control Card to transmit input signals to the SLCC, enabling communication and coordination between these two components. It relies on these inputs to perform its control functions effectively.

- 10PL Connector: This connector serves as the interface for input/output (I/O) signals between the LAN I/O Terminal Board and the Card. It enables communication between the LAN card and the LAN I/O Terminal Board, facilitating the exchange of data and signals over the network. This connector plays a vital role in integrating the LAN Card into the networked system and allows for remote monitoring and control capabilities.

- ARCPL Connector: The ARCPL connector establishes input/output (I/O) connections between the DLAN (Distributed Local Area Network) and ARCNET signals and the Card. This connector allows for the transmission of signals related to DLAN and ARCNET protocols, enabling communication with other devices or systems utilizing these protocols. It provides connectivity options for specific network configurations or protocols employed in the system.

- KPPL Connector: The KPPL connector facilitates input/output (I/O) connections between the Programmer Module keypad and the Card. It enables the exchange of data and signals between the card and the Programmer Module keypad. This connector allows the user to input commands, configurations, or other instructions through the keypad, which are then processed and executed.

Board Mounting

- Features four standoffs that serve as mounting points. Standoffs are small supports or spacers that elevate and secure the board in a fixed position. These standoffs provide stability and ensure proper alignment between the module and the surrounding components or enclosure.

- Includes a connector labeled KPPL, which is designed to accept a programmer module plug. The programmer module plug is a specific type of connector that allows for communication and interaction. When the programmer module plug is connected to the KPPL connector, it establishes a physical and electrical connection between the LAN Card and the programmer module.

- Covered by the keypad and cover module. This module is specifically designed to provide a protective enclosure and to house the keypad interface. The keypad allows users to input commands, configurations, or other instructions, facilitating control and interaction with the module. The cover module is shielded from external elements and provides a secure housing for the keypad and other components.

Application Data

Includes configurable hardware that must be set correctly for the application:

- Berg-type Hardware Jumpers: The configurable hardware includes Berg-type hardware jumpers, which are identifiable by the JP nomenclature. These jumpers are physical connectors that can be manually adjusted or moved to establish or break connections on the device. The JP nomenclature provides a standardized way of labeling and identifying these jumpers.

- Wire Jumpers: In addition to the hardware jumpers, the device also utilizes wire jumpers, which are identified by the WJ nomenclature. Wire jumpers consist of physical wires that are used to create connections between specific points on the device. Similar to hardware jumpers, wire jumpers offer flexibility in configuring the device's circuitry.

Software

- The LAN Control Processor (LCP) software contained in EPROMs U6 and U7 cannot be configured in the field.

- The EPROMs U6 and U7 can be replaced and moved from one board to another. When ordering replacement boards. The EPROMs from the old board must be transferred to the new board.

- When replacing an SLCC (or LCC) and the EPROMs are required, specify it to ensure that both EPROMs are included.

- The use of software-implemented fault tolerance (SIFT) technology in the Mark V TMR control system. Based on separate inputs, each control processor in a TMR control panel determines its own control and protection functions. The control processors vote on the inputs used to make these decisions individually. If one control processor fails to correctly read an input, the erroneous value is out-voted.

Software Design

- The exciter application program is made up of useful software modules that work together as building blocks to meet system demands. Variables are kept in random-access memory (RAM), whereas block definitions and configuration information are saved in read-only memory (ROM) (RAM).

- The code is executed by microcontrollers. Traditional analog controls are simulated by the exciter application program. The program makes use of an open architecture system and a library of pre-existing building blocks.

- Each block serves a specific purpose, such as signal level detectors, function generators, proportional integral (PI) regulators, AND gates, and function generators.

Time synchronization

- Time synchronization allows for the accurate synchronization of all Mark V control panels on the Stagelink with a global time source (GTS), such as an IRIG-B time code signal or periodic pulse inputs. This enables the GTS to set the time clocks of all computers with operator interfaces.

- The rest of the plant's equipment, including the DCSs, should be synchronized to this common GTS.

Power Requirements

- The Mark V panel can accept power from a variety of sources. Before entering the Mark V panel, each power input source (dc and two alternating current sources) should be fed through its own external 30 A 2 pole thermal magnetic circuit breaker. A 125 V dc source and/or up to two 120/240 V ac sources can be used as power sources.

- Each core in the panel has its own power supply board, which is powered by a 125 V dc panel distribution bus.

Characteristics

- Critical Communication: Turbine control systems require highly reliable and low-latency communication to ensure the safe and efficient operation of the turbine. LAN Communications Cards are specifically engineered to meet these stringent communication requirements.

- Redundancy: Redundancy is often a critical feature in turbine control systems to ensure continued operation even in the event of hardware failures. LAN Communications Cards may support features like dual NICs (Network Interface Cards) or redundant network paths to enhance system reliability.

- Industrial-Grade: Turbine control environments can be harsh, with factors like temperature variations, vibrations, and electromagnetic interference. LAN Communications Cards used in such systems are typically built to withstand these harsh conditions and are designed to be rugged and durable.

- Protocol Support: Turbine control systems may use specific communication protocols or standards. LAN Communications Cards are designed to support these protocols, ensuring seamless integration with the control system and other devices on the network.

- Security: Security is a paramount concern in critical systems like turbine control. These cards may include security features such as hardware encryption, firewall capabilities, and support for secure communication protocols to protect against unauthorized access or tampering.

- Monitoring and Diagnostics: Advanced LAN Communications Cards for turbine control systems often include diagnostic and monitoring features. These features allow for real-time monitoring of network performance and card health, aiding in the early detection of issues.

- Integration with SCADA Systems: Turbine control systems are often part of larger Supervisory Control and Data Acquisition (SCADA) systems. LAN Communications Cards facilitate the seamless integration of turbine data into the SCADA network, allowing for centralized monitoring and control.

WOC is happy to assist you with any of your automation requirements. Please contact us by phone or email for pricing and availability on any parts and repairs.

FREQUENTLY ASKED QUESTIONS

What is DS215SLCCG1AZZ01B?

It is a LAN Communications Card developed by GE

What is the main microprocessor on the board?

The main microprocessor on the board is the LAN Control Processor (LCP), which is located on U1. The LCP communicates with the Drive Control Processor (DCP) on the Drive Control Card via 3PL and dual-ported RAM (U5).

What should be done when ordering replacement boards that require the EPROMs U6 and U7?

When ordering replacement boards that require the EPROMs U6 and U7, the EPROMs from the old board must be transferred to the new board.

What should be specified when replacing an SLCC (or LCC) and the EPROMs are required?

When replacing an SLCC (or LCC) and the EPROMs are required, a SLCC should be specified to ensure that both EPROMs are included.

How is the programmer module connected to this LAN Communications Card, and what does it control?

The programmer module is connected to the card via the KPPL connector. It interfaces with the 16-position alphanumeric display and display controller and plays a key role in controlling and configuring the LAN Communications Card.

What is the LAN Control Processor (LCP), and what are its main components?

The LAN Control Processor (LCP), represented by U1, serves as the main microprocessor. It is equipped with replaceable EPROMs (U6 and U7) and specific memory components (U8 and U9) that house the LCP software and data.

How does communication occur between the LCP and the Drive Control Processor (DCP)?

Communication between the LCP and the DCP on the Drive Control Card is facilitated through 3PL and dual-ported RAM (U5). Dual-ported RAM allows two microprocessors to access memory independently and concurrently.

What is the significance of the triple modular redundant (TMR) design in the Mark V control system?

The TMR design enhances unit reliability by employing three redundant control processors. In the event of a control processor failure, the system can safely continue to operate, control, and protect the unit without shutdown, ensuring uninterrupted performance.